## 『清华信息大讲堂』第 66 讲—Intel 论坛第五讲

| 报告题目:         | Multi-Core vs. Multi-thread, Cache vs. non-<br>Cache, Homogenous vs. Heterogeneous<br>systems: Initial Thoughts |

|---------------|-----------------------------------------------------------------------------------------------------------------|

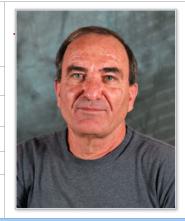

| 报告人:          | Dr. Uri Weiser                                                                                                  |

|               | Israel Institute of Technology                                                                                  |

| 报告时间:         | 2010-11-15, 15:00-16:00                                                                                         |

| 报告地点:         | FIT 1-315                                                                                                       |

| A la adama ad |                                                                                                                 |

## **Abstract:**

Computational requirement is characterized by a wide range of diverse applications. In many cases these applications coexist and run simultaneously on a specific system. The applications differ from each other by their practical requirements e.g. performance, BW, latency, power limitation, performance/power requirement, QoS, differential services etc. Essentially, these requirements are heterogynous and calls for reciprocal HW/OS implementation to enable a better fit to the applications' need.

We will present the current "Homogenous" Multi-Core vs. Multi-thread solutions. We will define the cache purpose in a Multi-Thread environment and suggest some new research directions.

On the other hand, device's power limitation will drive for Heterogeneous HW. We will raise questions regarding: HW/OS Heterogeneous approach, Data Content based requirements, Heterogeneous Processing elements (cores), same ISA/Different ISA?, how should the applications' Scheduling work? Well, no simple answers.

In this talk we will try to open a small windows to several research topics we are conducting today and present some questions and few answers. The talk seeks to stimulate discussion, debate and future work.

## **Biography:**

**Dr. Uri Weiser** is a visiting Professor at the Electrical Engineering department, the Technion IIT (Israel Institute of Technology) and act as an advisor of numerous startups. He received the bachelor and master degrees in EE from the Technion and Ph.D in CS from the University of Utah, Salt Lake City.

Uri worked at Intel from 1988-2006. At Intel, Uri initiated the definition of the Pentium® processor, drove the definition of Intel's MMX<sup>TM</sup> technology, invented the Trace Cache, established as a co-managed the Intel Microprocessor Design Center at Austin, Texas and initiated an Advanced Media applications research activity. Uri was appointed as Intel Fellow in 1996, in 2002 he became an IEEE Fellow and in 2005 an ACM Fellow.

Prior to his career at Intel, Uri worked for the Israeli Department of Defense as a research and system engineer and later with National Semiconductor Design Center in Israel, where he led the design of the NS32532 microprocessor.

Uri was an Associate Editor of IEEEMicro Magazine (1992-2004) and is Associate Editor of Computer Architecture Letters.

主办单位:信息科学技术学院

联系人: 陈文光 (62783505)